AMD SP7 и SP8 — новые серверные платформы с поддержкой DDR5 и PCIe 6.0 для процессоров EPYC Venice и Verano

На серверном горизонте — важные новинки от AMD. Компания недавно анонсировала свои будущие процессоры EPYC Venice и EPYC Verano, а вместе с ними рассекретила платформы SP7 и SP8, которые для новых чипов станут своеобразной «опорой». Эти платформы обещают серьёзный скачок по части производительности, коммуникаций и пропускной способности, поддерживая ультрасовременную память DDR5 и скоростной интерфейс PCI Express 6.0. Что это значит для дата-центров и корпоративных решений, и в чем основные отличия от прошлых поколений — разберёмся.

EPYC Venice и Verano: краткая справка

AMD EPYC Venice — это процессоры на базе архитектуры Zen 6C с внушительным количеством ядер — до 256 на одной связке CCD (Core Complex Die). Запуск запланирован ориентировочно на 2026 год. Какие-то детали по архитектуре Verano пока держатся в секрете, однако предполагается, что это может быть либо усовершенствованный Zen 6, либо новая архитектура Zen 7, появление которой ожидается в 2027 году.

Для сравнения: нынешнее поколение EPYC Turin, построенное на Zen 5, предлагает до 192 ядер (12 CCD), а Venice с 256 ядрами — это качественный переход, как с точки зрения вычислительной мощности, так и энергоэффективности.

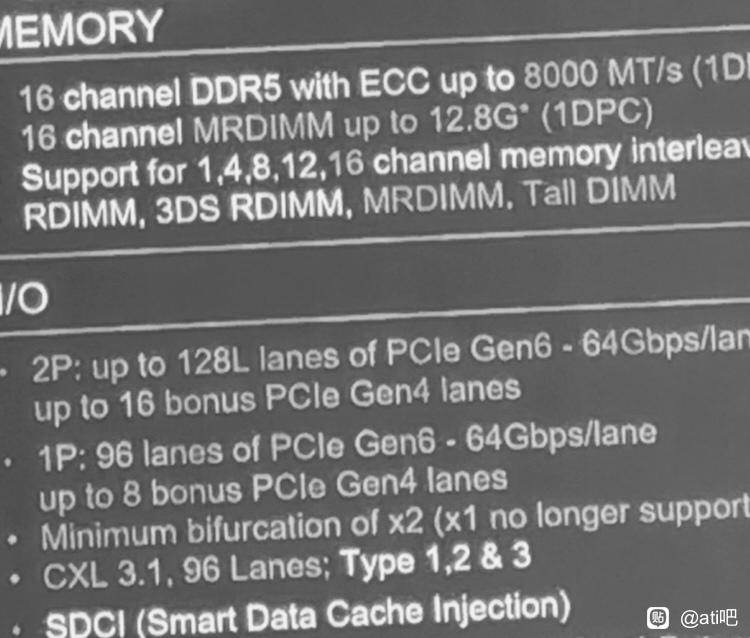

Платформа SP7 — всё для высоких нагрузок

SP7 позиционируется как флагманская серверная платформа для масштабных вычислительных центров и крупных предприятий. Основные особенности:

- Память DDR5 с 16 каналами: поддержка скоростей до 8000 MT/s (миллионов транзакций в секунду) для error-correcting code (ECC) памяти, а в конфигурациях MRDIMM (multi-rank DIMM — многорейтинговые модули) — до 12 800 MT/s в конфигурации 1DPC (один модуль на канал).

- Широкий выбор типов модулей: RDIMM, 3DS RDIMM (с 3D-стековыми чипами для плотности), MRDIMM и Tall DIMM (высокие модули памяти), что позволит подобрать оптимальную конфигурацию под задачи заказчика.

- Поддержка двухпроцессорных систем (2P): на одной материнской плате могут устанавливаться два процессора с общим доступом к ресурсам.

- 128 линий PCIe 6.0 — это около 64 Гбит/с на линию (вдвое быстрее предыдущего поколения PCIe 5.0). Плюс ещё 16 дополнительных линий PCIe 4.0, которые можно использовать для менее требовательных устройств.

- В версии с одним процессором (1P) предлагается до 96 линий PCIe 6.0 и 8 линий PCIe 4.0.

- Поддержка инновационной технологии Smart Data Cache Injection (SDCI), позволяющей повысить эффективность обработки данных за счет интеллектуального управления кэш-памятью.

Источник изображения: Baidu Forums

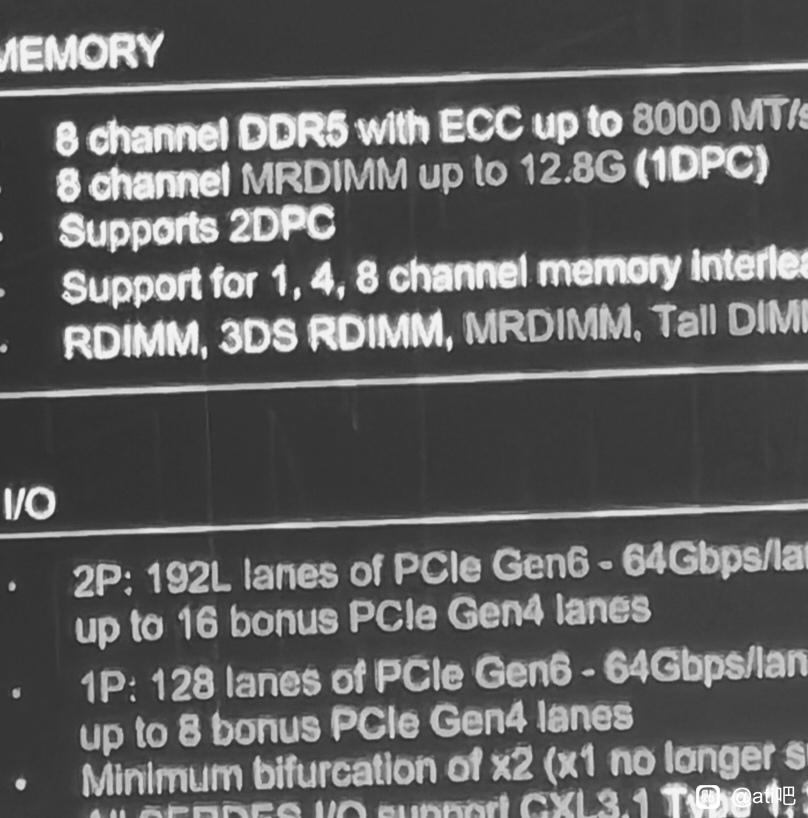

Платформа SP8 — доступное решение с большим количеством линий PCIe

SP8 нацелена на сегмент младших и средних серверов, сохраняя поддержку чипов следующего поколения EPYC. Отличия от SP7:

- Поддержка DDR5 памяти с 8 каналами, что в два раза меньше, чем у SP7, но всё ещё значительно больше, чем у многих конкурентов.

- Увеличенное количество линий PCIe 6.0: до 192 линий на 2P-системах (против 128 у SP7) и до 128 линий в однопроцессорных конфигурациях. Большое число линий хорошо подходит для серверов, где требуется много подключения к сетевым адаптерам, NVMe-накопителям и прочему периферийному оборудованию.

- Платформа остаётся достаточно мощной для широкого спектра задач благодаря высокой пропускной способности и гибкой настройке подсистемы ввода-вывода.

Источник изображения: Baidu Forums

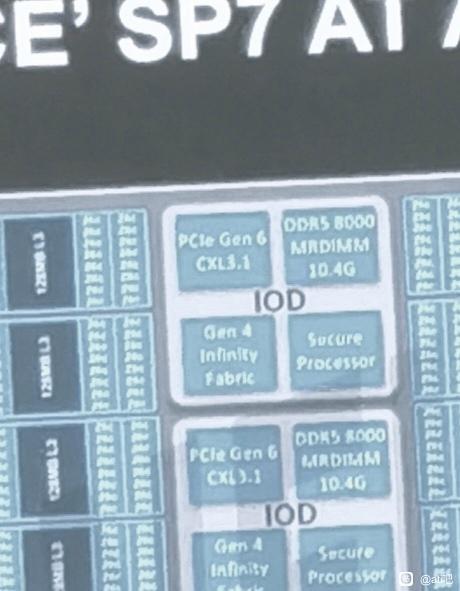

Архитектура и конфигурация процессоров

Zen 6C в EPYC Venice — технология с чиплетным дизайном. Ниже основные детали:

- До 32 ядер на каждый CCD (ядро — это базовый элемент процессора). Всего таких CCD у Venice может быть восемь, что и даёт суммарные 256 ядер.

- 1 ГБ L3-кеша — огромный объём для серверных чипов, который помогает ускорить обработку данных и снизить задержки.

- Два IO-дайса (Input/Output) обеспечивают поддержку PCIe Gen 6.0 и CXL 3.1 — новейшего стандарта для ускоренной связи между компонентами внутри системы, а также поддержку быстрых DDR5-8000.

- Реализован интерфейс Infinity Fabric Gen4, обеспечивающий эффективный обмен данными между кластерами ядер и подсистемой ввода-вывода.

- Встроенный безопасный процессор (Secure Processor) отвечает за защиту данных и предотвращение атак на уровне железа.

Источник изображения: Baidu Forums

Для сравнения, классические EPYC Venice с архитектурой Zen 6 (не «Dense») предлагают 12 ядер на CCD и 8 таких CCD, итого до 96 ядер и 192 потока — примерно столько же, сколько сейчас у EPYC Turin.

Что это значит для российского рынка?

AMD уверенно продолжает наступление в сегменте серверных решений, где конкуренция с Intel и другими игроками крайне напряжённая. Рост числа ядер и линии PCIe 6.0 обеспечат компаниям из России и СНГ возможность строить более мощные и эффективные дата-центры для облачных услуг, больших вычислений и искусственного интеллекта.

На сегодня цены на серверные EPYC могут варьироваться — учитывая текущие рыночные условия и курсы валют, средняя цена топовых моделей Venice с 256 ядрами может достигать около 1,5–2 млн рублей. Платформы SP7 и SP8 ориентированы на крупные компании и провайдеров облачных услуг, где инвестиции обоснованы высокой производительностью и надёжностью.

Возможная доступность в России будет зависеть от международной ситуации и политики компании AMD, но учитывая значимость серверных решений и спрос на них, ожидать релиза официальных продуктов в российских дата-центрах стоит.

Итоги и прогнозы

- SP7 задаёт высочайший стандарт с 16 каналами памяти DDR5 и до 128 PCIe 6.0 линий — идеален для самых тяжёлых вычислительных задач.

- SP8 предлагает оптимальное соотношение цены и производительности с 8 каналами DDR5 и рекордными 192 линиями PCIe 6.0 в двухпроцессорной конфигурации.

- Новые EPYC Venice с Zen 6C смогут похвастаться впечатляющей производительностью — до 256 ядер и гигабайтным кэшем L3.

- EPYC Verano обещает ещё больше инноваций с архитектурой Zen 7, выход которой запланирован на 2027 год.

AMD продолжает демонстрировать серьёзный технологический рывок, задавая новые стандарты для серверного рынка. Это подарит ИТ-индустрии России (и всего мира) инструменты для создания более мощных, эффективных и масштабируемых дата-центров будущего.

Таблица: семейства процессоров AMD EPYC

| Семейство EPYC | Verano | Venice | Turin-X | Turin-Dense | Turin | Siena | Bergamo | Genoa-X | Genoa | Milan-X | Milan | Rome | Naples |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Название | EPYC 9007 | EPYC 9006 | EPYC 9005 | EPYC 9005 | EPYC 9005 | EPYC 8004 | EPYC 9004 | EPYC 9004 | EPYC 9004 | EPYC 7004 | EPYC 7003 | EPYC 7002 | EPYC 7001 |

| Год выхода | 2027 | 2026 | 2025 | 2025 | 2024 | 2023 | 2023 | 2023 | 2022 | 2022 | 2021 | 2019 | 2017 |

| Архитектура | Zen 7 | Zen 6 | Zen 5 | Zen 5C | Zen 5 | Zen 4 | Zen 4C | Zen 4 V-Cache | Zen 4 | Zen 3 | Zen 3 | Zen 2 | Zen 1 |

| Техпроцесс | TBD | 2 нм TSMC | 4 нм TSMC | 3 нм TSMC | 4 нм TSMC | 5 нм TSMC | 4 нм TSMC | 5 нм TSMC | 5 нм TSMC | 7 нм TSMC | 7 нм TSMC | 7 нм TSMC | 14 нм GloFo |

| Платформа | SP7 | SP7 | SP5 | SP5 | SP5 | SP6 | SP5 | SP5 | SP5 | SP3 | SP3 | SP3 | SP3 |

| Сокет | TBD | TBD | LGA 6096 | LGA 6096 | LGA 6096 | LGA 4844 | LGA 6096 | LGA 6096 | LGA 6096 | LGA 4094 | LGA 4094 | LGA 4094 | LGA 4094 |

| Макс. число ядер | TBD | 96 | 128 | 192 | 128 | 64 | 128 | 96 | 96 | 64 | 64 | 64 | 32 |

| Макс. число потоков | TBD | 192 | 256 | 384 | 256 | 128 | 256 | 192 | 192 | 128 | 128 | 128 | 64 |

| Макс. объём L3 кеша | TBD | TBD | 1536 МБ | 384 МБ | 384 МБ | 256 МБ | 256 МБ | 1152 МБ | 384 МБ | 768 МБ | 256 МБ | 256 МБ | 64 МБ |

| Поддержка памяти | TBD | DDR5-12800 | DDR5-6000? | DDR5-6400 | DDR5-6400 | DDR5-5200 | DDR5-5600 | DDR5-4800 | DDR5-4800 | DDR4-3200 | DDR4-3200 | DDR4-3200 | DDR4-2666 |

| Каналы памяти | TBD | 16 (SP7) | 12 (SP5) | 12 | 12 | 6 | 12 | 12 | 12 | 8 | 8 | 8 | 8 |

| PCIe | TBD | 128-192 Gen6 | TBD | 128 Gen5 | 128 Gen5 | 96 Gen5 | 128 Gen5 | 128 Gen5 | 128 Gen5 | 128 Gen4 | 128 Gen4 | 128 Gen4 | 64 Gen3 |

| TDP | TBD | ~600 Вт | 500 Вт | 450-500 Вт | 320-400 Вт | 70-225 Вт | 320 Вт | 400 Вт | 400 Вт | 280 Вт | 280 Вт | 280 Вт | 200 Вт |

AMD готовит большие перемены — следите за обновлениями, и мы обязательно расскажем, как новые серии EPYC поменяют рынок серверного железа в России и мире.

Одна вещь очевидна: эра гигаядер и сверхскоростных интерфейсов уже не за горами.

Автор: [Ваше имя], эксперт и журналист в области компьютерных технологий.